productes Categoria

- transmissor FM

- 0-50w 50w-1000w 2kw-10kw 10kw +

- transmissor de TV

- 0-50w 50-1kw 2kw-10kw

- antena FM

- antena de TV

- antena accessori

- cable connector divisor de l'energia càrrega fictícia

- RF Transistor

- Font d'alimentació

- Equips d'àudio

- DTV Front Equip Fi

- Sistema d'enllaç

- sistema de STL sistema d'enllaç de microones

- ràdio FM

- Mesurador de potència

- altres Productes

- Especial per a Coronavirus

productes Etiquetes

llocs FMUSER

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> afrikaans

- sq.fmuser.net -> Albanès

- ar.fmuser.net -> Àrab

- hy.fmuser.net -> Armeni

- az.fmuser.net -> Azerbaidjanès

- eu.fmuser.net -> basc

- be.fmuser.net -> bielorús

- bg.fmuser.net -> Bulgària

- ca.fmuser.net -> català

- zh-CN.fmuser.net -> Xinès (simplificat)

- zh-TW.fmuser.net -> Xinès (tradicional)

- hr.fmuser.net -> croata

- cs.fmuser.net -> txec

- da.fmuser.net -> Danès

- nl.fmuser.net -> Holandès

- et.fmuser.net -> estonià

- tl.fmuser.net -> filipí

- fi.fmuser.net -> finès

- fr.fmuser.net -> Francès

- gl.fmuser.net -> gallec

- ka.fmuser.net -> georgià

- de.fmuser.net -> alemany

- el.fmuser.net -> Grec

- ht.fmuser.net -> crioll haitià

- iw.fmuser.net -> Hebreu

- hi.fmuser.net -> Hindi

- hu.fmuser.net -> Hungarian

- is.fmuser.net -> islandès

- id.fmuser.net -> indonesi

- ga.fmuser.net -> irlandès

- it.fmuser.net -> Italià

- ja.fmuser.net -> japonès

- ko.fmuser.net -> coreà

- lv.fmuser.net -> Letó

- lt.fmuser.net -> Lituània

- mk.fmuser.net -> macedoni

- ms.fmuser.net -> Malai

- mt.fmuser.net -> maltès

- no.fmuser.net -> Noruega

- fa.fmuser.net -> persa

- pl.fmuser.net -> Polonès

- pt.fmuser.net -> Portuguès

- ro.fmuser.net -> Romanès

- ru.fmuser.net -> rus

- sr.fmuser.net -> serbi

- sk.fmuser.net -> Eslovac

- sl.fmuser.net -> Eslovènia

- es.fmuser.net -> Castellà

- sw.fmuser.net -> Suahili

- sv.fmuser.net -> Suec

- th.fmuser.net -> Tai

- tr.fmuser.net -> turc

- uk.fmuser.net -> ucraïnès

- ur.fmuser.net -> urdú

- vi.fmuser.net -> Vietnamita

- cy.fmuser.net -> gal·lès

- yi.fmuser.net -> Yiddish

Què és Half Subtractor: Working and its Applications, K-MAP, Circuit using NAND Gate

Date:2021/10/18 21:55:58 Hits:

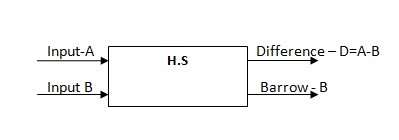

Per processar la informació com la llum o el so d’un punt a un altre, podem utilitzar circuits analògics donant entrades adequades en forma de senyals analògics. En aquest procés, hi ha probabilitats de captació de soroll pels senyals analògics d’entrada i això pot provocar pèrdues en el senyal de sortida, vol dir que qualsevol entrada que estem processant al nivell d’entrada no és igual a l’etapa de sortida. Per superar, s’implementen aquests circuits digitals. El circuit digital es pot dissenyar amb portes lògiques. Les portes lògiques són un circuit electrònic que realitza operacions lògiques basades en les seves entrades i dóna a la sortida un sol bit, ja sigui baix (Lògica 0 = tensió zero) o alt (Lògica 1 = alta tensió). Els circuits combinacionals es poden dissenyar amb més d'una porta lògica. Aquests circuits són ràpids i independents del temps, sense retroalimentació entre entrada i sortida. Els circuits combinacionals són útils per a operacions aritmètiques i booleanes. Els millors exemples de circuits combinacionals inclouen mitja sumadora, sumadora completa, mitja subtractora, resta completa, multiplexors, demultiplexors, codificador i descodificador. Què és Half Subtractor? s'utilitza per restar els dos bits de l'entrada. Aquí la sortida del subtractor depèn purament de les entrades actuals i no depèn de les etapes anteriors. Les sortides de mitja subtracció són diferència i barrow. És similar a la resta arthimètica en què si el subtrahend és més gran que el minuend aniríem per un préstec B = 1 o bé el préstec seguiria sent zero B = 0. Per entendre-ho millor, entrem a la taula de veritat que es mostra a continuació.  half-subtractor-block-diagram La taula de veritat La taula de veritat half-subtractor mostra els valors de sortida segons les entrades que s’apliquen a les etapes d’entrada. La taula de la veritat es divideix en dues parts. La part esquerra es denota com a etapa d’entrada i la part dreta com a etapa de sortida. Als circuits digitals, l’entrada 0 i l’entrada 1 indiquen la lògica baixa i la lògica alta. Segons la configuració, la lògica baixa significa voltatge zero, la lògica alta significa alta tensió (com ara 5V, 7V, 12V, etc.). Entrades Sortides Entrada - A Entrada - BD diferència -DBarrow - B 000010 1001111100 Taula de veritat Explicació Quan les entrades A i B són zero, les sortides del substractor D i B també són zero. Quan l’entrada A és alta i B és zero la diferència és Alta és a dir, 1 i Barrow és zero Quan l’entrada A és zero i l’entrada B és alta, les sortides de D i B són elevades amb les respectives. Quan ambdues entrades són altes, les dues sortides del mig restador són zero. De la taula de veritat anterior, podem Trobeu l’equació de la diferència (D) i Barrow (B). Equacions de la diferència-D: la diferència és alta quan les entrades A = 1, B = 0 i A = 0, B = 1. A partir d'aquesta afirmació D = AB '+ A'B = A⊕B. Segons l’equació D, denota l’ex o porta.D = A⊕B Equacions per Barrow-B: Barro només és elevat quan l’entrada A és baixa i B és alta. A partir d'aquest punt, l'equació de Barrow B serà, B = A'BB = A'B A partir de les diferències i equacions de barrow anteriors, podem dissenyar el diagrama de circuits de mitja substracció utilitzant el mapa K -MapK - MapKarnaugh simplifica l'expressió d'àlgebra de Boole per al circuit mitjà de la substracció. Aquest és el mètode oficial per trobar l'equació de l'àlgebra de Boole per a qualsevol circuit. Resolvem les expressions booleanes del circuit de la resta de restes mitjançant K-map. K-Map for Difference (D) i Barrow (B)

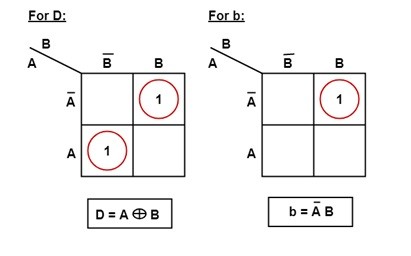

half-subtractor-block-diagram La taula de veritat La taula de veritat half-subtractor mostra els valors de sortida segons les entrades que s’apliquen a les etapes d’entrada. La taula de la veritat es divideix en dues parts. La part esquerra es denota com a etapa d’entrada i la part dreta com a etapa de sortida. Als circuits digitals, l’entrada 0 i l’entrada 1 indiquen la lògica baixa i la lògica alta. Segons la configuració, la lògica baixa significa voltatge zero, la lògica alta significa alta tensió (com ara 5V, 7V, 12V, etc.). Entrades Sortides Entrada - A Entrada - BD diferència -DBarrow - B 000010 1001111100 Taula de veritat Explicació Quan les entrades A i B són zero, les sortides del substractor D i B també són zero. Quan l’entrada A és alta i B és zero la diferència és Alta és a dir, 1 i Barrow és zero Quan l’entrada A és zero i l’entrada B és alta, les sortides de D i B són elevades amb les respectives. Quan ambdues entrades són altes, les dues sortides del mig restador són zero. De la taula de veritat anterior, podem Trobeu l’equació de la diferència (D) i Barrow (B). Equacions de la diferència-D: la diferència és alta quan les entrades A = 1, B = 0 i A = 0, B = 1. A partir d'aquesta afirmació D = AB '+ A'B = A⊕B. Segons l’equació D, denota l’ex o porta.D = A⊕B Equacions per Barrow-B: Barro només és elevat quan l’entrada A és baixa i B és alta. A partir d'aquest punt, l'equació de Barrow B serà, B = A'BB = A'B A partir de les diferències i equacions de barrow anteriors, podem dissenyar el diagrama de circuits de mitja substracció utilitzant el mapa K -MapK - MapKarnaugh simplifica l'expressió d'àlgebra de Boole per al circuit mitjà de la substracció. Aquest és el mètode oficial per trobar l'equació de l'àlgebra de Boole per a qualsevol circuit. Resolvem les expressions booleanes del circuit de la resta de restes mitjançant K-map. K-Map for Difference (D) i Barrow (B) Mapa K per a la diferència (D) i Barrow (B) Segons el mapa K, el primer implicant és A'B i el segon implicant és AB '. Quan simplifiquem aquestes dues equacions implicants, obtindrem l'equació simplificada per a la diferència de DD = A'B + AB'Lavors, D = A⊕B. Aquesta equació simplement indica la porta Ex-OR. Per trobar l’expressió booleana simplificada per a la carreta B, hem de seguir el mateix procés que hem seguit per a la diferència D. Per tant, B = A’B. Les portes NOR s’anomenen portes universals. Aquí, la porta NAND s’anomena porta universal perquè podem dissenyar qualsevol tipus de circuit digital utilitzant combinacions de n nombre de portes NAND. A causa d’aquesta especialitat, la porta NAND s’anomena porta universal. Ara, dissenyem un circuit de mitja substracció mitjançant portes NAND.

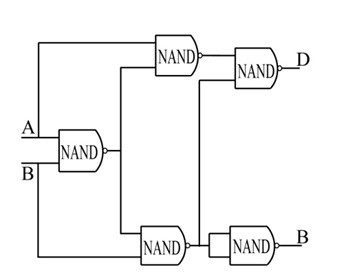

Mapa K per a la diferència (D) i Barrow (B) Segons el mapa K, el primer implicant és A'B i el segon implicant és AB '. Quan simplifiquem aquestes dues equacions implicants, obtindrem l'equació simplificada per a la diferència de DD = A'B + AB'Lavors, D = A⊕B. Aquesta equació simplement indica la porta Ex-OR. Per trobar l’expressió booleana simplificada per a la carreta B, hem de seguir el mateix procés que hem seguit per a la diferència D. Per tant, B = A’B. Les portes NOR s’anomenen portes universals. Aquí, la porta NAND s’anomena porta universal perquè podem dissenyar qualsevol tipus de circuit digital utilitzant combinacions de n nombre de portes NAND. A causa d’aquesta especialitat, la porta NAND s’anomena porta universal. Ara, dissenyem un circuit de mitja substracció mitjançant portes NAND. mig-substracte-implementat-amb-portes-NAND Podem dissenyar el circuit de mig substracte amb cinc portes NAND. Considereu A i B com a entrades a la primera etapa de la porta NAND, la seva sortida de nou connectada com una entrada a la segona porta NAND així com la tercera porta NAND. Segons les seves entrades, dóna la sortida i en l'etapa final de les portes NAND, la sortida diferencial D i la sortida B barrow estaran a la seva sortida. L'equació de sortida de la diferència D final és D = A EquB i equació de barrow B com a B = A'B. Mitjançant l'ús de diferents combinacions de portes NAND per construir el substractor, les equacions finals de diferència i barrow seran D = A⊕B i B = A'B només. de Half Subtractor Hi ha diverses aplicacions d’aquests subtractors. Pràcticament són senzills d’analitzar. Alguns d’ells s’enumeren de la següent manera: per restar els nombres presents en la posició més baixa a les columnes, es prefereixen aquests subtractors. La Unitat Aritmètica i Lògica (ALU) present al processador prefereix aquesta unitat per restar. En funció de l’operació necessària, el mitjà substractor té la capacitat d’augmentar o disminuir el nombre d’operadors.Les mitges substraccions s’utilitzen a l’amplificador. Mentre transmeten els senyals d’àudio s’utilitzen per evitar les distorsions. Circuit de mitja resta. En condicions en temps real, no es pot restar múltiples nombres de bits mitjançant mitges restadores. Aquest inconvenient es pot superar utilitzant el subtractor complet.

mig-substracte-implementat-amb-portes-NAND Podem dissenyar el circuit de mig substracte amb cinc portes NAND. Considereu A i B com a entrades a la primera etapa de la porta NAND, la seva sortida de nou connectada com una entrada a la segona porta NAND així com la tercera porta NAND. Segons les seves entrades, dóna la sortida i en l'etapa final de les portes NAND, la sortida diferencial D i la sortida B barrow estaran a la seva sortida. L'equació de sortida de la diferència D final és D = A EquB i equació de barrow B com a B = A'B. Mitjançant l'ús de diferents combinacions de portes NAND per construir el substractor, les equacions finals de diferència i barrow seran D = A⊕B i B = A'B només. de Half Subtractor Hi ha diverses aplicacions d’aquests subtractors. Pràcticament són senzills d’analitzar. Alguns d’ells s’enumeren de la següent manera: per restar els nombres presents en la posició més baixa a les columnes, es prefereixen aquests subtractors. La Unitat Aritmètica i Lògica (ALU) present al processador prefereix aquesta unitat per restar. En funció de l’operació necessària, el mitjà substractor té la capacitat d’augmentar o disminuir el nombre d’operadors.Les mitges substraccions s’utilitzen a l’amplificador. Mentre transmeten els senyals d’àudio s’utilitzen per evitar les distorsions. Circuit de mitja resta. En condicions en temps real, no es pot restar múltiples nombres de bits mitjançant mitges restadores. Aquest inconvenient es pot superar utilitzant el subtractor complet.

Deixa un missatge

Llista de missatges

Comentaris Loading ...